Podstawy

techniki mikroprocesorowej

Architektury

mikroprocesorów

Wydział Elektroniki Mikrosystemów i Fotoniki

dr inż. Piotr Markowski

Na prawach rękopisu.

Budowa mikrokontrolera

ATmega8535

CPU - Central Processing Unit Procesor

A B A B A B A

Status Register

I – obsługa przerwań on/off

T – bit magazynujący (sTorage)

H – Half carry – przeniesienie z bitu 3 przy op. arytmet. S – Sign - XOR flag N i V

V – zmiana z 01111111 na 10000000 N – gdy MSB = 1

Z – gdy 00000000

C – Carry – przeniesienie

Procesor jednocyklowy

Procesor wielocyklowy

ATmega8535

Porty I/O

Urządzenia peryferyjne CPU

Pamięć ATmega8535

Pamięć programu – FLASH EEPROM, 8 kB – kod programu Pamięć danych – SRAM, 512 B – bieżące dane tymczasowe

rejestry

Pamięć dodatkowa, użytkownika – EEPROM, 512 B

Pamięć programu – FLASH EEPROM

• zorganizowana jako 4 K x 16 bajtów ($FFF)

• podzielona na PROGRAM SECTION oraz BOOT SECTION

• przechowuje program załadowany do mikrosterownika

Pamięć programu – licznik rozkazów

Program Counter –

11 10 9 8 7 6 5 4 3 2 1 0 PC

(FLASH EEPROM $000 - $FFF)

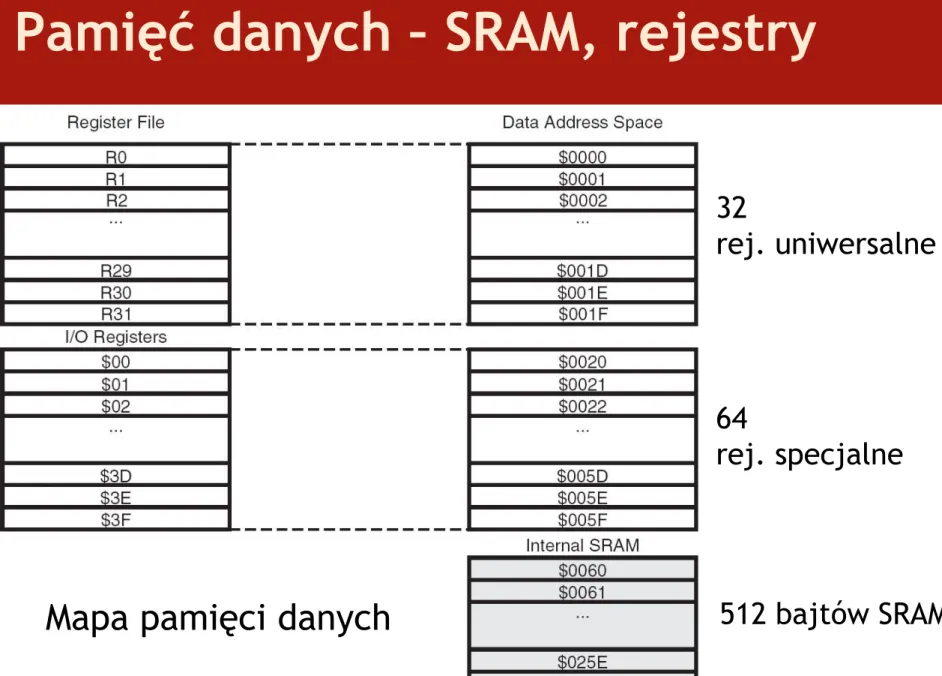

Pamięć danych – SRAM, rejestry

Mapa pamięci danych

32

rej. uniwersalne

64

rej. specjalne

512 bajtów SRAM

SRAM

Stos –

Wskaźnik stosu (Stack Pointer) – wskazuje

Wierzchołek stosu SPL, SPH

512 wierszy, 512 kB Dekrementacja SP

Konieczna inicjalizacja stosu

Rejestry

Rejestry specjalne:

– do sterowania urządzeniami wewnętrznymi - 64 szt. (str. 299)

- nazwy to skróty (SREG = Status Register) Rejestry uniwersalne:

- do wykonywania operacji (arytmetycznych, logicznych itp.) - 32 szt.

- nazwy: R0 – R31 (w tym X, Y, Z)

Architektura komputerów

Podział ze względu na strukturę pamięci:

Podział ze względu na instrukcje procesora:

Architektura komputerów:

von Neumanna

Pierwsza architektura komputerowa, rok 1945. Jedna pamięć dla danych i programu.

ALU

układ sterujący

CPU

Architektura komputerów:

Harwardzka

Oddzielne

Prostsza budowa (w stosunku do von Neumanna). ALU

układ sterujący

CPU

AVR – mapy pamięci

32 rej. uniwersalne 64 rej. specjalne 512 bajtów SRAM 0 31 0 63 0 511 RAMENDArchitektura komputerów:

von Neumanna vs Harwardzka

von Neumanna Harwardzka

Architektura komputerów:

zmodyfikowana Harwardzka

ALU układ sterujący CPU PróbaArchitektura komputerów

Podział ze względu na strukturę pamięci:

Podział ze względu na instrukcje procesora:

Architektura komputerów:

CISC (Complex Instruction Set Computer)

lata ‘60 XX wieku (droga pamięć - trzeba ją oszczędzać)Stosowane:

rodzina procesorów x86 (PC) R8C25 (Renesas)

Architektura komputerów:

RISC (Reduced Instruction Set Computer)

80% instrukcji CISC było nieużywanepoczątek lat ’70 XX wieku – wdrożenie koncepcji RISC (projekt IBM 801)

Stosowane przeszłość: Amiga, MAC (ustąpiły CISC)

obecnie: smartfony, tablety, mikrokontrolery

(ARM7) (PIC, AVR)

CISC vs RISC

PC PM D µPC µPM Dµ wykonanie instr. (cykle zegarowe) PC PM D IR wykonanie instr. (cykle zegarowe) MIKROPROG RA M INSTRUKCJE WYKONYWANE PRZEZ HARDWARECISC vs RISC

- Kompleksowy zestaw instrukcji, wielocyklowe - Instrukcje zamieniane na

mikroprogram

- Każda instr. może odnosić się do pamięci

- Różne formaty instrukcji - Brak potoków

- Wiele trybów adresowania pamięci

- Proste instrukcje, jednocyklowe

- Instrukcje wykonywane przez hardware

- Tylko LOAD/STORE odnoszą się do pamięci

- Jeden format instrukcji - Potoki

- Niewiele trybów

adresowania pamięci

CISC vs RISC

- Mało rejestrów - Dużo rejestrów

- więcej linii kodu - nawet 4x szybszy

- Mniej tranzystorów, niższa cena

CISC vs RISC

1 2 3 4 1 2 3 Pamięć R1 R2CISC vs RISC

100101101101110 001001111011100 100101101101110 001001111011100 001001111011100 100101101101110 110101100010011 110111010111001 010101100010011 110111010111001 10011011101101101111011101 00110111001111011100110110 01110111011101100110100110 11110111011100110011100110 10110110011011001101101110 1011100RISC

RISC – potoki (pipeline)

Czas

Czas

RISC – potoki (pipeline)

Zwiększają szybkość procesorów RISC

Pob Dek Wyk Pam Z

Pob – pobranie instrukcji Dek – dekodowanie instr. Wyk – wykonanie instr. Pam – dostęp do pamięci Z – zapis wyniku

RISC – potoki (pipeline)

Krok potoku Cykl zegarowy

1 2 3 4 5 6

Pobranie LDI ADD

Dekodowanie LDI ADD

Wykonanie LDI ADD

Pamięć LDI ADD

Zapis LDI ADD

RISC – potoki (pipeline)

Krok potoku Cykl zegarowy

1 2 3 4 5 6

Pobranie LDI ADD

Dekodowanie LDI ADD

Wykonanie LDI ADD

Pamięć LDI ADD

Zapis LDI ADD

LDI R16,105 BRNE etykieta ADD R16,R18

RISC – potoki (pipeline)

Liczba kroków potoku: klasycznie:

AVR, PIC: Intel Xeon:

Xelerated X10q Network Processor: Po co tyle??

Procesor „fully pipelined”

CISC vs RISC

- Mało rejestrów - Dużo rejestrów

- więcej linii kodu - nawet 4x szybszy

- Mniej tranzystorów, niższa cena

ATmega8535 - CPU

CPU:

• Jednostka Arytmetyczno-Logiczna (ALU) • Rejestry uniwersalne

• Status Register (SREG) • Wskaźnik Stosu (SP) • Licznik rozkazów (PC) RISC architektura Harwardzka rodzina AVR typ ATmega 1-poziomowy potok